IA32 Paging Architecture

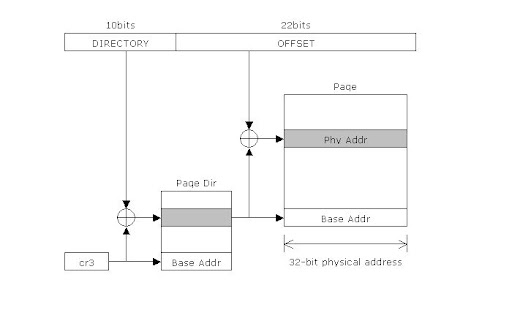

Paging Unit:將線性位址(Linear Address,或稱作虛擬位址Virtual Address)轉換成實體位址的功能單元。

在 i386 的系統裡面,因為是 32-bit CPU 的關係,所以最多只能定址到 4GB 的虛擬記憶體。定址方式總共有四種:

Register points to page table

什麼是 PAE 呢?

在 Intel 的 64 and IA-32 Architectures Software Developer's Manual 裡面給的定義如下:

「Physical Address Extension. Physical addresses greater than 32 bits are supported: extended page table entry formats, an extra level in the page translation tables is defined, 2-Mbyte pages are supported instead of 4 Mbyte pages if PAE bit is 1. The actual number of address bits beyond 32 is not defined, and is implementation specific.」

簡單來說,就是一套讓32bit CPU能夠定址到大於 4GB 的記憶體位址。在Intel的實作裡面,就是把原先 page table 中的 2 個 entries 當成一個 entry 來用,所以從原來的 32bit 延伸到 64bit。不過這裡要注意的是,雖然有 64 bit,不過其實只使用了 36 bit,剩下的 28bit 為 reserved,也就是說記憶體只能支援到 64GB。

Page Directory Entry & Page Table Entry 的欄位詳細資料

下面兩張圖是 IA32 中規定,在 Page Directory Entry 和 Page Table Entry 的詳細欄位。要注意的事,下面兩張圖都是在 PAE disabled 的情況下。不過即使是 PAE enabled,欄位內容依然一樣,只是 Base Address 擴增到 24 bits。

Page Directory Entry

Page Table Entry

在 i386 的系統裡面,因為是 32-bit CPU 的關係,所以最多只能定址到 4GB 的虛擬記憶體。定址方式總共有四種:

- 4KB/page without PAE enabled

- 4MB/page without PAE enabled

- 4KB/page with PAE enabled

- 2MB/page with PAE enabled

Register points to page table

什麼是 PAE 呢?

在 Intel 的 64 and IA-32 Architectures Software Developer's Manual 裡面給的定義如下:

「Physical Address Extension. Physical addresses greater than 32 bits are supported: extended page table entry formats, an extra level in the page translation tables is defined, 2-Mbyte pages are supported instead of 4 Mbyte pages if PAE bit is 1. The actual number of address bits beyond 32 is not defined, and is implementation specific.」

簡單來說,就是一套讓32bit CPU能夠定址到大於 4GB 的記憶體位址。在Intel的實作裡面,就是把原先 page table 中的 2 個 entries 當成一個 entry 來用,所以從原來的 32bit 延伸到 64bit。不過這裡要注意的是,雖然有 64 bit,不過其實只使用了 36 bit,剩下的 28bit 為 reserved,也就是說記憶體只能支援到 64GB。

Page Directory Entry & Page Table Entry 的欄位詳細資料

下面兩張圖是 IA32 中規定,在 Page Directory Entry 和 Page Table Entry 的詳細欄位。要注意的事,下面兩張圖都是在 PAE disabled 的情況下。不過即使是 PAE enabled,欄位內容依然一樣,只是 Base Address 擴增到 24 bits。

Page Directory Entry

Page Table Entry

留言

張貼留言